Home >> Blog >> verilog 語法教學

verilog 語法教學

Verilog 是一種硬體描述語言 (HDL)。它是一種用於描述數字系統的語言,例如網絡交換機、微處理器、存儲器或觸發器。我們可以在任何級別使用 HDL 來描述任何數字硬體。用 HDL 描述的設計獨立於技術,非常易於設計和調試,通常比原理圖更有用,特別是對於大型電路。

什麼是 Verilog?

Verilog是一種硬體描述語言(HDL),用於描述數字系統,例如網絡交換機或微處理器或存儲器觸發器。

開發Verilog是為了簡化流程並使 HDL 更加健壯和靈活。今天,Verilog 是整個半導體行業使用和實踐的最流行的 HDL。

HDL旨在通過允許工程師描述所需硬體的功能並讓自動化工具將該行為轉換為實際的硬體元素(如組合門和時序邏輯)來增強設計過程。

Verilog 與任何其他硬體描述語言一樣。它允許設計人員以自下而上或自上而下的方法設計設計。

- 自底向上設計:傳統的電子設計方法是自底向上。每個設計都使用標準門在門級執行。這種設計提供了一種設計新的結構、分層設計方法的方法。

- 自上而下的設計:它允許早期測試、不同技術的輕鬆更改和結構化系統設計,並提供許多其他好處。

Verilog 抽象級別

Verilog 支持多個抽象級別的設計,例如:

- 行為層面

- 寄存器傳輸層

- 門級

行為層面

行為層通過並發算法描述一個系統的行為。每個算法都是順序的,這意味著它由一組一個一個執行的指令組成。函數、任務和塊是主要元素。沒有考慮設計的結構實現。

寄存器傳輸層

使用寄存器傳輸級別的設計使用操作和寄存器之間的數據傳輸來指定電路的特性。

RTL 程式碼的現代定義是“任何可合成的程式碼都稱為 RTL 程式碼”。

門級

系統的特性由邏輯鏈路及其在邏輯級別內的時序屬性來描述。所有信號都是離散信號。它們只能有明確的邏輯值(“0”、“1”、“X”、“Z”)。

可用的操作是預定義的邏輯原語(基本門)。門級建模可能不是邏輯設計的正確想法。門級程式碼是使用綜合工具等工俱生成的,他的網表用於門級仿真和後端。

Verilog 的歷史

- Verilog HDL 的歷史可以追溯到 1980 年代,當時一家名為 Gateway Design Automation 的公司開發了一種邏輯仿真器 Verilog-XL 和一種硬體描述語言。

- Cadence Design Systems 於 1989 年收購了 Gateway,並獲得了語言和模擬器的使用權。1990 年,Cadence 將該語言納入公共領域,目的是使其成為一種標準的、非專有語言。

- Verilog HDL 現在由非營利組織 Accellera 維護,該組織由 Open Verilog International (OVI) 和 VHDL International 合併而成。OVI 的任務是讓語言通過 IEEE 標準化程序。

- 1995 年 12 月,Verilog HDL 成為 IEEE Std。1364-1995。2001 年發布了一個重大修訂的版本:IEEE Std。1364-2001。2005 年進行了進一步修訂,但這只是增加了一些小改動。

- Accellera 還開發了一個新標準 SystemVerilog,它擴展了 Verilog。

- SystemVerilog 於 2005 年成為 IEEE 標準 (1800-2005)。

Verilog 有什麼用處?

Verilog 創建了一個抽象級別,有助於隱藏其實現和技術的細節。

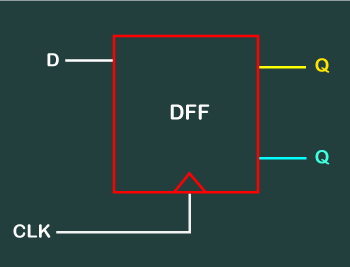

例如,D 觸發器設計需要了解如何安排晶體管以實現上升沿觸發的 FF,以及將值鎖存到觸發器上所需的上升、下降和 CLK-Q 時間。許多其他面向技術的細節。

功耗、時序以及驅動網絡和其他觸發器的能力也需要對晶體管的物理特性有更透徹的了解。

Verilog 幫助我們專注於行為,其餘的留待以後整理。

先決條件

在學習 Verilog 之前,您應該具備 VLSI 設計語言的基本知識。

- 您應該了解邏輯圖的工作原理、布爾代數、邏輯門、組合電路和順序電路、運算符等。

- 您應該了解靜態時序分析概念,例如設置時間、保持時間、關鍵路徑、時鐘頻率限制等。

- SIC 和 FPGA 基礎知識以及綜合和仿真概念。

觀眾

我們的 Verilog 教學旨在幫助願意學習如何在 Verilog HDL 中對數字系統進行建模以實現自動綜合的初學者、SEO搜尋引擎優化工程師和驗證工程師。在本教學結束時,您將獲得 Verilog 的中級專業知識。